# Side-Channel Analysis Resistant Implementation of AES on Automotive Processors

Master Thesis Ruhr-University Bochum

Chair for Embedded Security Prof. Dr.-Ing. Christof Paar

from Andreas Hoheisel June 12, 2009

Co-Advised by: Dipl.-Ing. Timo Kasper (Ruhr-University Bochum) Dr. Torsten Schütze (Robert Bosch GmbH, CR/AEA)

## Statement

I hereby declare, that the work presented in this master thesis is my own work and that to the best of my knowledge it is original, except where indicated by references to other authors.

# Erklärung

Hiermit versichere ich, dass ich meine Master Thesis selber verfasst und keine anderen als die angegebenen Quellen und Hilfsmittel benutzt, sowie Zitate kenntlich gemacht habe.

Bochum, den 12. Juni 2009

Andreas Hoheisel

# Contents

| Gl  | ossar                             | y                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                            |                       |                                         |                                  |                     |   | i                                                                                                          |

|-----|-----------------------------------|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------------------------|----------------------------------|---------------------|---|------------------------------------------------------------------------------------------------------------|

| Lis | st of                             | Tables                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                            |                       |                                         |                                  |                     |   | vii                                                                                                        |

| Lis | st of                             | Figures                                                |                                                                                                                                                                                                                                                                                                                                                                                                                            |                       |                                         |                                  |                     |   | ix                                                                                                         |

| 1   | <b>Intro</b><br>1.1<br>1.2<br>1.3 | oductio<br>Motiva<br>Advers<br>Scope                   |                                                                                                                                                                                                                                                                                                                                                                                                                            |                       |                                         |                                  | •                   | • | <b>1</b><br>1<br>2<br>3                                                                                    |

| 2   | AES<br>2.1<br>2.2<br>2.3          | Introd<br>Mathe                                        | anced Encryption Standarductionmatical Backgroundmatical Backgroundnentation AspectsMicrocontroller ModelMicrocontroller ModelThe Key Schedule8-bit Software Implementation Straight from the Standard8-bit Optimized Software Implementation32-bit Software Implementation32-bit T-Tables Implementation32-bit Implementation with Transposed StateHardware ImplementationsComparison of Different Implementation Options | · · · · · · · · · · · | - · · · · · · · · · · · · · · · · · · · | · · ·<br>· · ·<br>· · ·<br>· · · | · · · · · · · · · · |   | 15<br>16<br>19<br>20<br>20                                                                                 |

| 3   | 3.1<br>3.2<br>3.3                 | Timing<br>3.1.1<br>3.1.2<br>3.1.3<br>Simple<br>Differe | <b>Pel Analysis</b> g Analysis         Evaluation of Timing Analysis Resistance         Two Sample T-Test         Timer's F-Test         Fisher's F-Test         Power Analysis         ential and Correlation Power Analysis <b>Persent AES Implementation</b>                                                                                                                                                            |                       | • •                                     | · ·                              |                     |   | <ul> <li>25</li> <li>25</li> <li>27</li> <li>27</li> <li>28</li> <li>30</li> <li>30</li> <li>33</li> </ul> |

|     | 4.1<br>4.2                        | Rando                                                  | m Bits                                                                                                                                                                                                                                                                                                                                                                                                                     | •                     | •                                       | <br>                             | •                   |   | 33<br>34<br>34<br>36                                                                                       |

|   |                                                                                                                                 | 4.2.3 Perfectly Masking AES Inverter Against First-Order Side-Channel At-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <b>9</b> 0                                                                                                                                                                         |

|---|---------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 38                                                                                                                                                                                 |

|   |                                                                                                                                 | 4.2.4 Combined Masking in Tower Fields                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 40<br>42                                                                                                                                                                           |

|   | 19                                                                                                                              | 4.2.5 Masking the <i>MixColumns</i> Transformation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 42<br>42                                                                                                                                                                           |

|   | 4.3                                                                                                                             | Countermeasure: Randomization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 42<br>42                                                                                                                                                                           |

|   |                                                                                                                                 | 4.3.1 Shuffling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $\frac{42}{43}$                                                                                                                                                                    |

|   | 4 4                                                                                                                             | 4.3.2 Execution of Dummy Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -                                                                                                                                                                                  |

|   | $4.4 \\ 4.5$                                                                                                                    | Comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 44<br>46                                                                                                                                                                           |

| 5 |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 49                                                                                                                                                                                 |

| Ū | 5.1                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 49                                                                                                                                                                                 |

|   | 0.1                                                                                                                             | 5.1.1 Compiler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 50                                                                                                                                                                                 |

|   |                                                                                                                                 | 5.1.2 Simulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 51                                                                                                                                                                                 |

|   |                                                                                                                                 | 5.1.3 Evaluation Board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 51                                                                                                                                                                                 |

|   |                                                                                                                                 | 5.1.4 The Multi-Core Debug System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 51                                                                                                                                                                                 |

|   | 5.2                                                                                                                             | TriCore CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 51                                                                                                                                                                                 |

|   | 5.3                                                                                                                             | TriCore Instruction Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 54                                                                                                                                                                                 |

|   |                                                                                                                                 | 5.3.1 Load and Store Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 54                                                                                                                                                                                 |

|   |                                                                                                                                 | 5.3.2 Arithmetic Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 55                                                                                                                                                                                 |

|   |                                                                                                                                 | 5.3.3 Extract Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 56                                                                                                                                                                                 |

|   |                                                                                                                                 | 5.3.4 Address Arithmetic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 57                                                                                                                                                                                 |

|   | 5.4                                                                                                                             | Time Measurement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 57                                                                                                                                                                                 |

|   |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                    |

| _ | _                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                    |

| 6 | -                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 59                                                                                                                                                                                 |

| 6 | <b>Opt</b><br>6.1                                                                                                               | Implementation Constraints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 59                                                                                                                                                                                 |

| 6 | 6.1                                                                                                                             | Implementation Constraints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 59<br>59                                                                                                                                                                           |

| 6 | 6.1<br>6.2                                                                                                                      | Implementation Constraints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 59<br>59<br>60                                                                                                                                                                     |

| 6 | <ul><li>6.1</li><li>6.2</li><li>6.3</li></ul>                                                                                   | Implementation Constraints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 59<br>59<br>60<br>61                                                                                                                                                               |

| 6 | 6.1<br>6.2                                                                                                                      | Implementation Constraints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 59<br>59<br>60<br>61<br>61                                                                                                                                                         |

| 6 | <ul><li>6.1</li><li>6.2</li><li>6.3</li></ul>                                                                                   | Implementation Constraints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <ul> <li>59</li> <li>59</li> <li>60</li> <li>61</li> <li>61</li> <li>61</li> </ul>                                                                                                 |

| 6 | <ul><li>6.1</li><li>6.2</li><li>6.3</li></ul>                                                                                   | Implementation Constraints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <ol> <li>59</li> <li>59</li> <li>60</li> <li>61</li> <li>61</li> <li>61</li> <li>62</li> </ol>                                                                                     |

| 6 | <ul><li>6.1</li><li>6.2</li><li>6.3</li></ul>                                                                                   | Implementation Constraints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <ol> <li>59</li> <li>59</li> <li>60</li> <li>61</li> <li>61</li> <li>61</li> <li>62</li> <li>63</li> </ol>                                                                         |

| 6 | <ul><li>6.1</li><li>6.2</li><li>6.3</li><li>6.4</li></ul>                                                                       | Implementation Constraints6.1.1Validation TestsAvailable AES ImplementationsGeneral Optimizations HintsAES Optimizations for the TriCore6.4.1AddRoundKey6.4.2SubBytes and ShiftRows6.4.3MixColumns6.4.4Inverse MixColumns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <ol> <li>59</li> <li>59</li> <li>60</li> <li>61</li> <li>61</li> <li>61</li> <li>62</li> <li>63</li> <li>65</li> </ol>                                                             |

| 6 | <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> </ul>                                                                  | Implementation Constraints6.1.1Validation TestsAvailable AES ImplementationsGeneral Optimizations HintsAES Optimizations for the TriCore6.4.1AddRoundKey6.4.2SubBytes and ShiftRows6.4.3MixColumns6.4.4Inverse MixColumnsSize Comparison of Unprotected Implementations                                                                                                                                                                                                                                                                                                                                                                                                                                             | 59<br>59<br>60<br>61<br>61<br>61<br>61<br>62<br>63<br>65<br>65                                                                                                                     |

| 6 | <ul><li>6.1</li><li>6.2</li><li>6.3</li><li>6.4</li></ul>                                                                       | Implementation Constraints6.1.1Validation TestsAvailable AES ImplementationsGeneral Optimizations HintsAES Optimizations for the TriCore6.4.1AddRoundKey6.4.2SubBytes and ShiftRows6.4.3MixColumns6.4.4Inverse MixColumnsSize Comparison of Unprotected ImplementationsProtected AES Implementation                                                                                                                                                                                                                                                                                                                                                                                                                 | 59<br>59<br>60<br>61<br>61<br>61<br>62<br>63<br>65<br>65<br>66                                                                                                                     |

| 6 | <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> </ul>                                                                  | Implementation Constraints6.1.1Validation TestsAvailable AES ImplementationsGeneral Optimizations HintsAES Optimizations for the TriCore6.4.1AddRoundKey6.4.2SubBytes and ShiftRows6.4.3MixColumns6.4.4Inverse MixColumnsSize Comparison of Unprotected ImplementationsProtected AES Implementation6.6.1Masking the Optimized AES Implementation                                                                                                                                                                                                                                                                                                                                                                    | $59 \\ 59 \\ 60 \\ 61 \\ 61 \\ 61 \\ 62 \\ 63 \\ 65 \\ 65 \\ 66 \\ 66 \\ 66$                                                                                                       |

| 6 | <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> </ul>                                                                  | Implementation Constraints6.1.1Validation TestsAvailable AES ImplementationsGeneral Optimizations HintsAES Optimizations for the TriCore6.4.1AddRoundKey6.4.2SubBytes and ShiftRows6.4.3MixColumns6.4.4Inverse MixColumnsSize Comparison of Unprotected ImplementationsProtected AES Implementation                                                                                                                                                                                                                                                                                                                                                                                                                 | 59<br>59<br>60<br>61<br>61<br>61<br>62<br>63<br>65<br>65<br>66                                                                                                                     |

| 7 | <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> </ul>                                        | Implementation Constraints6.1.1Validation TestsAvailable AES ImplementationsGeneral Optimizations HintsAES Optimizations for the TriCore6.4.1AddRoundKey6.4.2SubBytes and ShiftRows6.4.3MixColumns6.4.4Inverse MixColumnsSize Comparison of Unprotected Implementations6.6.1Masking the Optimized AES Implementation6.6.2Size Comparison of Protected Implementations                                                                                                                                                                                                                                                                                                                                               | $59 \\ 59 \\ 60 \\ 61 \\ 61 \\ 61 \\ 62 \\ 63 \\ 65 \\ 65 \\ 66 \\ 66 \\ 66$                                                                                                       |

|   | <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> </ul>                                        | Implementation Constraints6.1.1Validation TestsAvailable AES ImplementationsGeneral Optimizations HintsAES Optimizations for the TriCore6.4.1AddRoundKey6.4.2SubBytes and ShiftRows6.4.3MixColumns6.4.4Inverse MixColumnsSize Comparison of Unprotected Implementations6.6.1Masking the Optimized AES Implementation6.6.2Size Comparison of Protected Implementations                                                                                                                                                                                                                                                                                                                                               | 59<br>59<br>60<br>61<br>61<br>61<br>62<br>63<br>65<br>65<br>66<br>66<br>72                                                                                                         |

|   | <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> <li>Imp</li> </ul>                           | Implementation Constraints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <ul> <li>59</li> <li>59</li> <li>60</li> <li>61</li> <li>61</li> <li>61</li> <li>62</li> <li>63</li> <li>65</li> <li>66</li> <li>66</li> <li>72</li> <li>75</li> </ul>             |

|   | <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> <li>Imp</li> <li>7.1</li> </ul>              | Implementation Constraints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <ul> <li>59</li> <li>59</li> <li>59</li> <li>60</li> <li>61</li> <li>61</li> <li>61</li> <li>62</li> <li>63</li> <li>65</li> <li>66</li> <li>66</li> <li>72</li> <li>75</li> </ul> |

|   | <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> <li>Imp</li> <li>7.1</li> <li>7.2</li> </ul> | Implementation Constraints         6.1.1       Validation Tests         Available AES Implementations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <ul> <li>59</li> <li>59</li> <li>59</li> <li>60</li> <li>61</li> <li>61</li> <li>62</li> <li>63</li> <li>65</li> <li>66</li> <li>66</li> <li>72</li> <li>75</li> <li>75</li> </ul> |

|   | <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> <li>Imp</li> <li>7.1</li> <li>7.2</li> </ul> | Implementation Constraints         6.1.1       Validation Tests         Available AES Implementations         General Optimizations Hints         AES Optimizations for the TriCore         6.4.1       AddRoundKey         6.4.2       SubBytes and ShiftRows         6.4.3       MixColumns         6.4.4       Inverse MixColumns         6.4.5       Size Comparison of Unprotected Implementations         Protected AES Implementation       6.6.1         Masking the Optimized AES Implementations       6.6.2         Size Comparison of Protected Implementations       6.6.2         Bementation Results       Measurement Setup         Runtime Comparison of the Implementations       Timing Analysis | <ul> <li>59</li> <li>59</li> <li>60</li> <li>61</li> <li>61</li> <li>62</li> <li>63</li> <li>65</li> <li>66</li> <li>66</li> <li>72</li> <li>75</li> <li>75</li> <li>77</li> </ul> |

# Glossary

| Notation           | <b>Description</b>                                   |

|--------------------|------------------------------------------------------|

| ACNS               | Applied Cryptography and Network Security Conference |

| AES                | Advanced Encryption Standard                         |

| cc                 | Cycle Count                                          |

| CMTF               | Combined Masking in Tower Fields                     |

| CPU                | Central Processing Unit                              |

| DPA                | Differential Power Analysis                          |

| ECU                | Electronic Control Units                             |

| ${ m GF} { m GPR}$ | Galois Field<br>General Purpose Registers            |

| IP                 | Integer Pipeline                                     |

| JTAG               | Joint Test Action Group                              |

| KAT                | Known Answer Tests                                   |

| LS                 | Load Store Pipeline                                  |

| LUT                | Lookup Table                                         |

| MCDS               | Multi-Core Debug System                              |

| MISRA              | Motor Industry Software Reliability                  |

| MSB                | Most Significant Bit                                 |

| NIST               | National Institute of Standards and Technology       |

| NOP                | No Operation                                         |

| PC                 | Program Counter                                      |

| PLL                | Phase-Locked Loop                                    |

| PMM                | Perfectly Masked Multiplication                      |

| PMS                | Perfectly Masked Squaring                            |

| RNG                | Random Number Generator                              |

| ROM                | Read Only Memory                                     |

# Notation Description

| SCA<br>SPA<br>splint<br>SPN | Side Channel Analysis<br>Simple Power Analysis<br>Secure Programming Lint<br>Substitution-Permutation Network |

|-----------------------------|---------------------------------------------------------------------------------------------------------------|

| TLU<br>TMM                  | Table lookup<br>Transformed Multiplicative Masking                                                            |

| UDE                         | Universal Debug Engine                                                                                        |

| VCO                         | Voltage Controlled Oscillator                                                                                 |

| XOR                         | exclusive OR                                                                                                  |

# List of Tables

| 2.1                                                                                                                               | Comparison between different unprotected AES software implementations $\ .$ .                                                                                                                                        | 23                                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| $4.1 \\ 4.2$                                                                                                                      | Number of random values required for secured implementation<br>Estimated memory consumption and cycle count for different AES implemen-                                                                              | 44                                                                                                                     |

| 4.3                                                                                                                               | tations with masking countermeasure, one mask / four masks $\ldots$ Comparison of an unmasked AES implementations with a masked and a masked and randomized AES implementation with $D$ dummy operations on an 8-bit | 45                                                                                                                     |

|                                                                                                                                   | smart card processors (AVR), Source: [HOM06]                                                                                                                                                                         | 47                                                                                                                     |

| $5.1 \\ 5.2$                                                                                                                      | Operation Modifiers                                                                                                                                                                                                  | $\begin{array}{c} 54 \\ 55 \end{array}$                                                                                |

| 6.1<br>6.2                                                                                                                        | Memory consumption comparison between the AES reference implementation<br>from Brijesh Singh and the Optimized TriCore implementation<br>Number of random values required for the protected AES Implementation wit   | 66                                                                                                                     |

| 6.3                                                                                                                               | additive masking                                                                                                                                                                                                     | $\begin{array}{c} 67\\72 \end{array}$                                                                                  |

| 6.4                                                                                                                               | Content of the data section for the protected AES Implementation with addi-<br>tive masking                                                                                                                          | 72                                                                                                                     |

| 6.5                                                                                                                               | Content of the data section for the protected AES Implementation with CMTF                                                                                                                                           | 73                                                                                                                     |

| 7.1                                                                                                                               | Comparison of runtime and program size between the different TriCore AES                                                                                                                                             |                                                                                                                        |

|                                                                                                                                   | implementations. The variable $D$ denotes the number of dummy operations                                                                                                                                             |                                                                                                                        |

| 79                                                                                                                                | for the protected AES implementation                                                                                                                                                                                 | $76 \\ 77$                                                                                                             |

| 7.2                                                                                                                               | for the protected AES implementation                                                                                                                                                                                 | 77                                                                                                                     |

| 7.3                                                                                                                               | for the protected AES implementation                                                                                                                                                                                 | 77<br>80                                                                                                               |

|                                                                                                                                   | for the protected AES implementation                                                                                                                                                                                 | 77                                                                                                                     |

| $7.3 \\ 7.4$                                                                                                                      | for the protected AES implementation                                                                                                                                                                                 | 77<br>80<br>80                                                                                                         |

| $7.3 \\ 7.4 \\ 7.5$                                                                                                               | for the protected AES implementation                                                                                                                                                                                 | 77<br>80<br>80<br>81                                                                                                   |

| 7.3<br>7.4<br>7.5<br>7.6                                                                                                          | for the protected AES implementation                                                                                                                                                                                 | 77<br>80<br>80<br>81<br>82<br>82                                                                                       |

| $7.3 \\ 7.4 \\ 7.5 \\ 7.6 \\ 7.7 \\ 7.8 $                                                                                         | for the protected AES implementation                                                                                                                                                                                 | 77<br>80<br>80<br>81<br>82                                                                                             |

| $7.3 \\ 7.4 \\ 7.5 \\ 7.6 \\ 7.7$                                                                                                 | for the protected AES implementation                                                                                                                                                                                 | 77<br>80<br>80<br>81<br>82<br>82<br>82                                                                                 |

| <ol> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>7.6</li> <li>7.7</li> <li>7.8</li> <li>7.9</li> </ol>                             | for the protected AES implementation                                                                                                                                                                                 | <ul> <li>77</li> <li>80</li> <li>80</li> <li>81</li> <li>82</li> <li>82</li> <li>82</li> <li>84</li> <li>85</li> </ul> |

| <ul> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>7.6</li> <li>7.7</li> <li>7.8</li> <li>7.9</li> <li>7.10</li> </ul>               | for the protected AES implementation                                                                                                                                                                                 | 77<br>80<br>81<br>82<br>82<br>82<br>84<br>85<br>85                                                                     |

| <ul> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>7.6</li> <li>7.7</li> <li>7.8</li> <li>7.9</li> <li>7.10</li> <li>7.11</li> </ul> | for the protected AES implementation                                                                                                                                                                                 | <ul> <li>77</li> <li>80</li> <li>80</li> <li>81</li> <li>82</li> <li>82</li> <li>82</li> <li>84</li> <li>85</li> </ul> |

# List of Figures

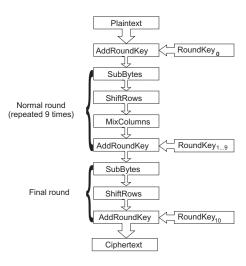

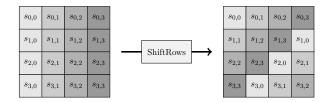

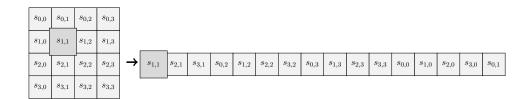

| <ol> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>2.5</li> <li>2.6</li> </ol> | Sequence of transformations used in an AES-128 encryptionMapping of input bytes to the State matrix and the output ciphertextThe SubBytes transformationThe ShiftRows transformationThe MixColumns transformationDecomposed SubBytes transformation | 6<br>6<br>7<br>7<br>8<br>13 |

|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

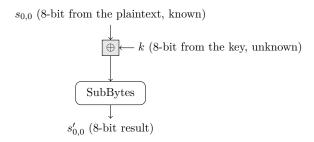

| 4.1                                                                                      | Initial AddRoundKey followed by the first SubBytes transformation in round one for one byte of the State matrix                                                                                                                                     | 33                          |

| 4.2                                                                                      | SubBytes transformation with masking countermeasure                                                                                                                                                                                                 | 36                          |

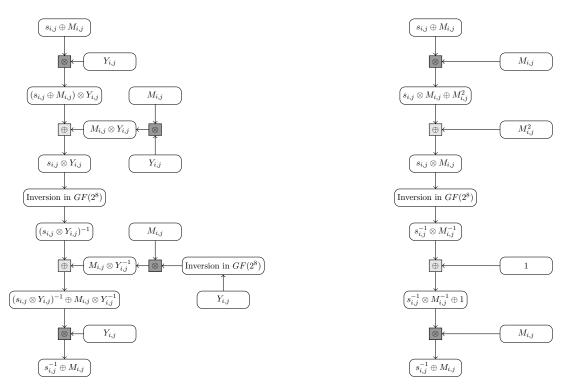

| 4.3                                                                                      | Multiplicative (left), Source: [AG01], and Simplified Multiplicative (right),<br>Source: [TSG02](right), Masked inversion in SubBytes                                                                                                               | 37                          |

| 4.4                                                                                      | Shuffled AES-State                                                                                                                                                                                                                                  | 42                          |

| 4.5                                                                                      | AES-State with dummy values                                                                                                                                                                                                                         | 43                          |

| 4.6<br>4.7                                                                               | AES-State with dummy values and shuffled AES-State                                                                                                                                                                                                  | 43<br>46                    |

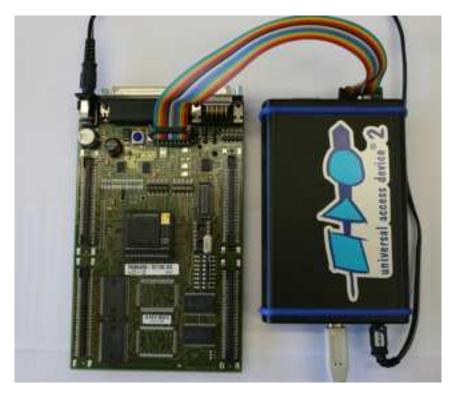

| 5.1                                                                                      | TriBoard – TC1796.303 on the left and AD2 on the right                                                                                                                                                                                              | 52                          |

| 5.2                                                                                      | MCDS config dialog                                                                                                                                                                                                                                  | 53                          |

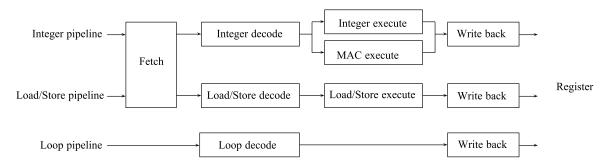

| 5.3                                                                                      | The three parallel pipelines of the execution unit                                                                                                                                                                                                  | 53                          |

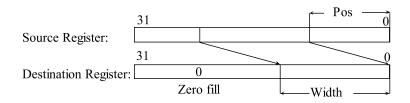

| 5.4                                                                                      | Operation of the EXTR.U instruction, source: [Inf07]                                                                                                                                                                                                | 56                          |

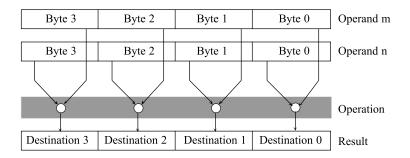

| 5.5                                                                                      | Packed Byte Data Format, source: [Inf07]                                                                                                                                                                                                            | 56                          |

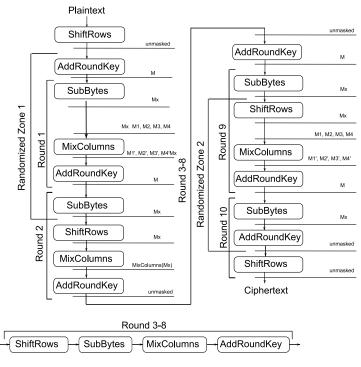

| 6.1                                                                                      | Protected AES                                                                                                                                                                                                                                       | 67                          |

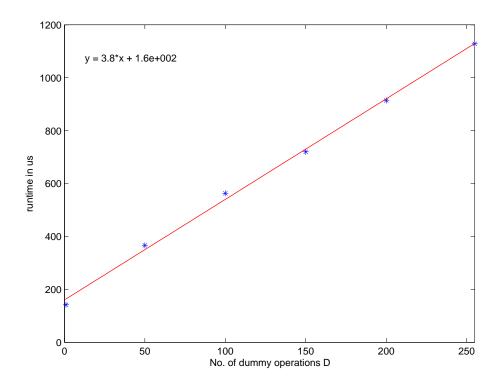

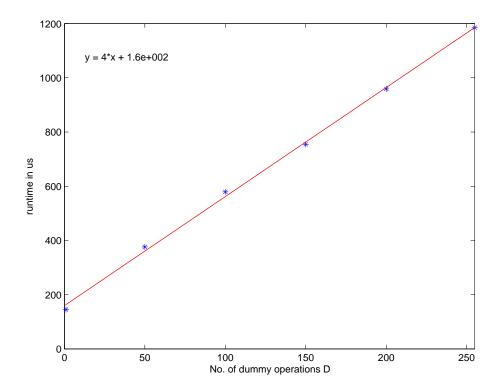

| 7.1                                                                                      | Runtime of the protected AES encryption with $1 \le D \le 255$ . The S-box is                                                                                                                                                                       |                             |

|                                                                                          | recalculated after every AES encryption                                                                                                                                                                                                             | 78                          |

| 7.2                                                                                      | Runtime of the protected AES decryption with $1 \le D \le 255$ . The S-box is recalculated after every AES decryption.                                                                                                                              | 78                          |

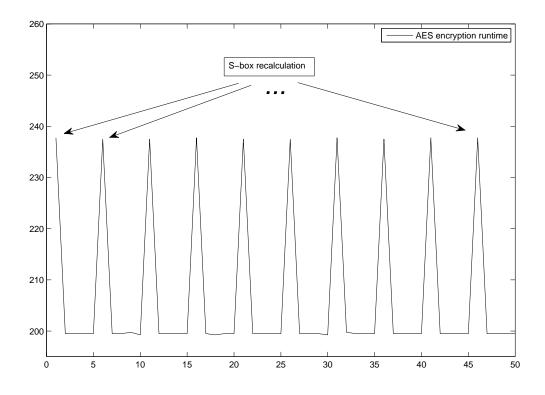

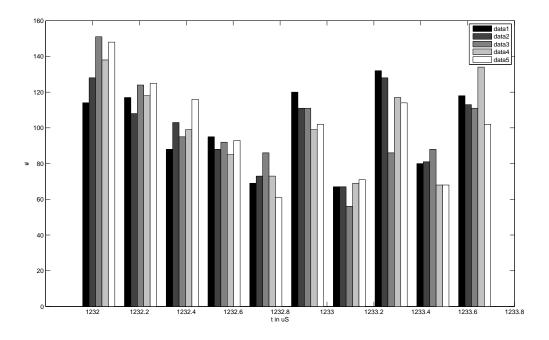

| 7.3                                                                                      | Runtime of the protected AES encryption with ten dummy operations (D=10).                                                                                                                                                                           | 10                          |

|                                                                                          | The S-box is recalculated after every $5^{th}$ AES encryption                                                                                                                                                                                       | 79                          |

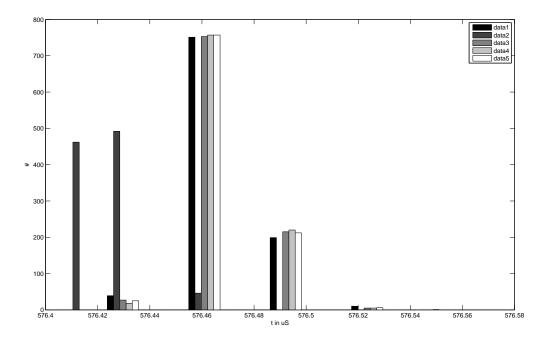

| 7.4                                                                                      | Histogram of the runtime for optimized AES implementation                                                                                                                                                                                           | 81                          |

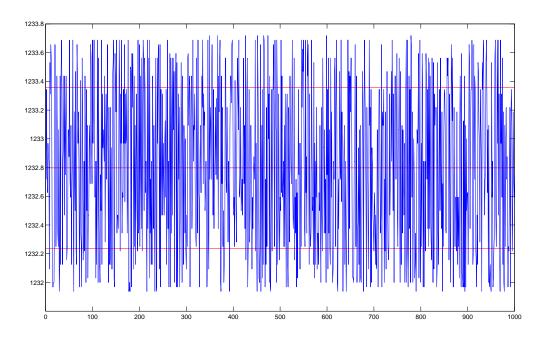

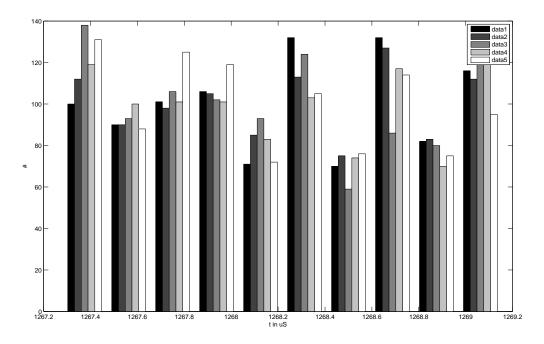

| 7.5                                                                                      | Runtime of the protected AES encryption (set four) with 16 dummy operations                                                                                                                                                                         |                             |

|                                                                                          | (D=16). The lines denote the mean (middle) and the variance of the runtime.                                                                                                                                                                         | 83                          |

| 7.6                                                                                      | Histogram of the runtime for protected AES encryption with 16 dummy oper-<br>ations (D=16)                                                                                                                                                          | 83                          |

| 7.7 | Histogram of the runtime for protected AES decryption with 16 dummy oper- |    |

|-----|---------------------------------------------------------------------------|----|

|     | ations $(D=16)$                                                           | 85 |

# Chapter 1

# Introduction

# 1.1 Motivation

Nowadays, security becomes more and more important in the automotive industry. Robert Bosch GmbH, Corporate Research supplies the necessary know-how and provides solutions for future applications in the business units.

Many functions in a modern car are realized with the help of software applications and the underlying electronics. This means in particular, that a growing part of the components in a car are realized through an easy to copy and manipulate software. Due to this fact, there is a growing need for an effective protection of these software applications to save the intellectual property on the one hand and to disclose manipulation, e.g., by tuning, on the other hand.

There are up to 80 electronic control units (ECU) built into a modern upper class car. These control units come from different suppliers, communicate over potentially insecure networks with each other and with the outside world respectively, e. g., with diagnostic equipment or in the near future Car2Car and Car2Infrastructure. As a consequence, these control units should authenticate each other and the communication data should be cryptographically protected against manipulation.

For several use cases in the automotive domain, e.g., tuning detection and sensor protection, cryptography constitutes a considerable part of the overall-security architecture. Due to their performance and compactness in implementations, symmetric encryption primitives are of special interest. These primitives can be used for attaining the following security goals:

- confidentiality: encryption of data,

- authenticity: challenge-response protocols,

- integrity: message authentication codes.

The State-of-the-Art symmetric encryption scheme is the Advanced Encryption Standard (AES), [FIP01]. This block cipher with key sizes of 128, 192, and 256 bits and a block size of 128 bits is remarkably fast and can be implemented very efficiently on a wide variety of platforms. It replaces the old Data Encryption Standard DES or, to be more precise, its variant Triple-DES.

A lot of proprietary mechanisms in the automotive environment are getting replaced by standardized security mechanisms. An example is here the changeover from the proprietary KeeLoq System<sup>1</sup>, which is used for keyless entry in cars and garage doors, to modern challenge-response protocols based on AES<sup>2</sup>.

<sup>1</sup> http://www.microchip.com

<sup>2</sup> Embedded AES-crypto engine for keyless entry systems, ESCAR2007.

# 1.2 Adversary Model and Assumptions

Ross Anderson and Markus Kuhn give a good classification of adversaries' knowledge, funding, and skills in [AK98]. They define the following three classes of attackers:

- Class I (clever outsiders): They are very intelligent but may have insufficient knowledge of the system. They may have access to only moderately sophisticated equipment. They often try to take advantage of an existing weakness in the system, rather than try to create one.

- Class II (knowledgeable insiders): They have substantial specialized technical education and experience. They have varying degrees of understanding of parts of the system but potential access to most of it. They have highly sophisticated tools and instruments for analysis.

- Class III (funded organizations): They are able to assemble teams of specialists with related and complementary skills backed by great funding resources. They can do in-depth analysis of the system, design sophisticated attacks, and use the most advanced analysis tools. They may use Class II Adversaries as part of the attack team.

We will focus on knowledgeable insiders, i. e., the cryptographic algorithm itself is known to the attack agent (no security by obscurity!). The attack agent may have access to equipment like oscilloscopes etc. that can be found in university labs. The specific implementation, e. g., the source code or an open sample device, is assumed to be *not available* to the attacker.

In terms of side-channel analysis resistance<sup>3</sup>, this means that our implementation should be resistant against:

- timing attacks, and

- first-order differential power analysis (DPA) attacks.

Resistance against timing attacks implies that we assume an adversary having access to an exact simulation of the runtime of the implementation. Note that we *do not require* resistance against the new microarchitectural side-channel attacks like cache and branch predication attacks [AKS07, Ber05, OST06, NS06]. This does not mean that these attacks may not be relevant, it just means that we think that an attack agent has no or only little chance to install a spy process on the target processor and to measure the timing signals with the necessary precision.<sup>4</sup>